# Deep level dopant compensated Czochralski silicon substrates for MMICs

Kanad Mallik<sup>1,2</sup>, A Abuelgasim<sup>1</sup>, P Ashburn<sup>1</sup>, and C H de Groot

<sup>1</sup> Nanoscale Systems Integration Group, School of Electronics and Computer Science, University of Southampton <sup>2</sup> Semiconductor Group, Department of Materials, University of Oxford

## Introduction

There has been a huge surge of activity in the development of on- and off-chip RF systems in recent years. Passive components like spiral inductors are essential and particularly problematic parts of these applications as not only do they take large real estate areas on the chips, they require considerable design and development time. That is why a proper understanding of the performance of spiral inductors, taking into consideration their interactions with the substrate material is important. The classical design trend is to try to isolate the effect of the substrate so that the de-embedded performance of the inductor may be realised, and leads to the prescription to fabricate the inductors as far away, or high up from the substrate as possible even at the cost of complications in the overall design. An obvious solution to this problem is to use high resistivity substrates for microwave applications. The fact that low-absorption, high resistivity substrates like alumina or sapphire and semi-insulating GaAs are very costly implies that affordable substrates like Czochralski silicon (Cz-Si) having optimal resistivity leading to reduced microwave absorption over 1 GHz would be the right choice. Cz-Si substrates in the resistivity range of 10-25  $\Omega$ cm are used in the microwave industry. However, it has been shown<sup>1</sup> that a substrate resistivity of at least 3 k $\Omega$ cm is required for optimum RF performance, and it has been suggested in the International Technology Roadmap of Semiconductors that Cz-Si substrates having resistivities > 10 k $\Omega$ cm would be considered as an emerging microwave substrate material<sup>2</sup>.

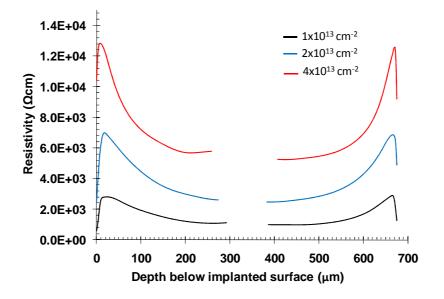

Fig. 1. A typical U-shaped spreading resistance profile of a 6-inch diameter high resistivity Czochralski silicon wafer produced by deep level gold doping compensation, showing the highly resistive surface layers of thickness up to 50  $\mu m$  and a relatively low-resistivity bulk region. The legend shows the gold implantation doses used.

We have recently demonstrated making Si substrates having a resistivity of more than 10 k $\Omega$ cm at room temperatures<sup>3</sup>, starting from nominally 50  $\Omega$ cm n-type Cz-Si with the help of deep level impurity compensation<sup>4</sup>. A typical spreading resistance profile of the material, measured at room temperatures has been shown in Fig. 1. This was produced by ion implanting Au and a subsequent in-diffusion anneal at 950 °C for 1 hr in Ar ambient. It is clearly seen that the highest resistivity achieved for a gold dose of  $4x10^{13}$  cm<sup>-2</sup> is 10 k $\Omega$ cm or more within a surface layer thickness of approximately 50  $\mu$ m from the front and back surfaces of the wafer. The material was tested for microwave attenuation in the range of 1-40 GHz using aluminium co-planar waveguides fabricated on it. The attenuation decreased from 1.6 to 0.6 dB/mm from the starting wafer (56  $\Omega$ cm) to the gold-doped high resistivity wafer (18 k $\Omega$ cm). The details of the work will be published elsewhere. The present article shows how this novel material is useful to enhance the performance of spiral inductors in terms of their key parameters, for example, the maximum quality factor (Q<sub>max</sub>), the frequency f<sub>max</sub> at which Q<sub>max</sub> is achieved, and the self-resonance frequency (SRF).

## Calculations

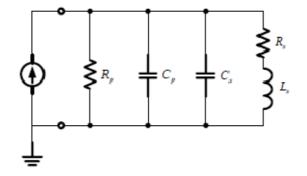

One of the effective analytical lumped parameter models<sup>5, 6</sup> of a spiral inductor that takes the finite conductivity of the substrate into account for the determination of its Q factor is shown in Fig. 2.

Fig. 2. The lumped circuit model of a one end grounded spiral inductor, taking into account the effects of the substrate resistance in the parameters,  $R_p$  and  $C_p$ .

The Q-factor, as a function of the angular frequency,  $\omega$  is given by

$$Q = \frac{\omega L_s}{R_s} \cdot \frac{R_p}{R_p + \left[ (\omega L_s / R_s)^2 + 1 \right] R_s} \cdot \left[ 1 - \frac{R_s^2 (C_s + C_p)}{L_s} - \omega^2 L_s (C_s + C_p) \right]$$

(1)

where  $L_S$ ,  $R_S$  and  $C_S$  are the inductance, series resistance and the capacitance, respectively of the metallic spiral while  $R_P$  and  $C_P$  represent the coupling resistance and capacitance of the inductor structure to the substrate. These are given by

$$R_{p} = \frac{1}{\omega^{2} C_{ox}^{2} R_{Si}} + \frac{R_{Si} (C_{ox} + C_{p})^{2}}{C_{ox}^{2}}$$

(2)

and

$$C_{p} = C_{ox} \cdot \frac{1 + \omega^{2} (C_{ox} + C_{Si}) C_{Si} R_{Si}^{2}}{1 + \omega^{2} (C_{ox} + C_{Si})^{2} R_{Si}^{2}}$$

(3)

where  $R_{Si}$ ,  $C_{Si}$  are resistance and capacitance of the silicon substrate, and  $C_{ox}$  is the capacitance of the oxide layer between the metallic spiral and the silicon substrate. Significantly, the analytical model of the spiral inductor indicates that the Q-factor of the spiral inductor is maximised when the coupling resistance  $R_p$  tends to infinity and this happens if the substrate resistance tends to either zero or infinity. This implies that the substrate resistance influences the behaviour of spiral inductors in competing ways, and lumped circuit modelling of spiral inductors is inadequate for a proper understanding.

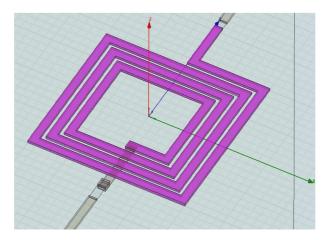

Fig. 3. The HFSS model of a 3-and-a-half turn spiral inductor used for calculation of different properties.

In this article we report calculations of the Q factor of spiral inductors in the frequency range of 1-40 GHz by modelling a hollow 3-and-a-half turn spiral inductor using a finite element (FE) full 3D high frequency electromagnetic simulator, HFSS v12.0. The parameters used in the simulation are listed in Table and the model is shown in Fig. 3. Two lumped ports with a common ground were introduced at the terminals of the inductor to excite the structure.

Table I. Dimensions of the 3-and-a-half turn hollow spiral inductor used in the HFSS simulation . The inductance, as calculated by the modified Wheeler formula<sup>7</sup> was 2.96 nH.

| Parameter                      | Value<br>(μm) |

|--------------------------------|---------------|

| Outermost arm length of spiral | 200           |

| Metal (AI) line width          | 10            |

| Line separation                | 5             |

| Spiral metal thickness         | 2             |

| Oxide thickness                | 5             |

| Underpass depth                | 2             |

| Underpass metal (AI) thickness | 0.5           |

| Silicon substrate thickness    | 500           |

The Q-factor was obtained from the Y-parameters, calculated in the driven modal solution scheme using the usual formula,

$$\boldsymbol{Q} = \left| \frac{im\left(\frac{1}{Y_{11}}\right)}{re\left(\frac{1}{Y_{11}}\right)} \right| \tag{4}$$

In FE calculations it is important to ensure convergence of the simulated results with respect to the simulation mesh. This was achieved here using the adaptive meshing feature of HFSS and selecting the convergence of the value of Q at 10 GHz with a tolerance of 5% during adaptive passes. Two successive converged adaptive passes were run to ensure that the solutions were stable. The effect of the resistivity variation was modelled first by a uniform and then a two-layer silicon substrate with a highly resistive surface layer just below the oxide layer, and a lower resistivity bulk region. The thicknesses and resistivities of both the surface region and the bulk were varied.

#### **Results and Discussions**

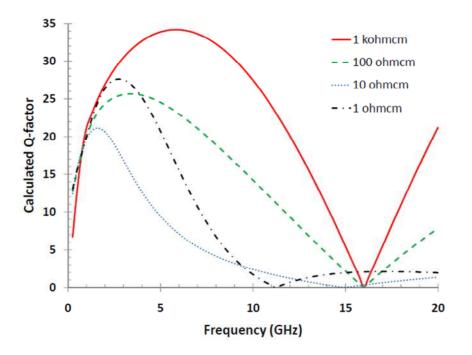

We show the effect of the substrate resistivity on the Q factor of a spiral inductor fabricated on a silicon wafer having a uniform resistivity in Fig. 4 as a function of the excitation frequency.

Fig. 4. The calculated Q-factor of the spiral inductor described in Table I and showed in Fig. 3 as a function of frequency with the resistivity of the 500  $\mu m$  thick silicon substrate varied from 1  $\Omega cm$  to 1 k $\Omega cm$ .

In this calculation the resistivity of the silicon substrate was varied in the range of 1  $\Omega$ cm to 1 k $\Omega$ cm. The general features of these simulated results agree well with calculated and experimental values of Q-factors obtained by other workers<sup>8, 9</sup> indicating the reliability of the simulations.

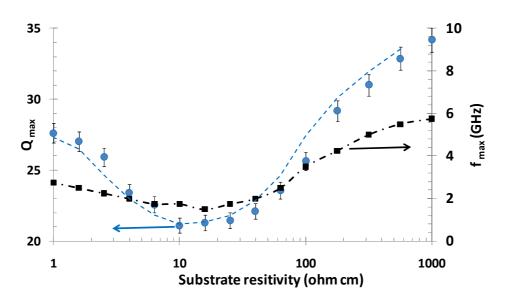

Fig. 5. The calculated values of  $Q_{max}$  (blue circles, dotted line) and  $f_{max}$  (black squares, dot-dash line) of the spiral inductor shown in Fig. 3 as functions of the uniform substrate resistivity.

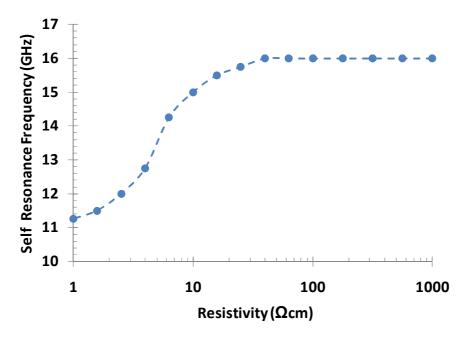

We clearly see that the Q factor is the highest for the highest substrate resistivity and falls with decrease in the latter, but improves again for a silicon resistivity of 1  $\Omega$ cm which is consistent with the trend suggested by Yue et. al.'s lumped circuit model<sup>5</sup> discussed earlier. The detailed nature of the variation of the maximum value of Q (Q<sub>max</sub>) and the frequency f<sub>max</sub> at which this occurs are shown in Fig. 5 as functions of the substrate resistivity. The values of Q<sub>max</sub> increase both for an increase and decrease in the substrate resistivity from around 10  $\Omega$ cm to 1 k $\Omega$ cm, and decrease to 1  $\Omega$ cm, respectively. However, Q<sub>max</sub> attains higher values for an increasing substrate resistivity and the trend for the f<sub>max</sub> is similar. The variation of SRF, the other important characteristic of spiral inductors with the substrate resistivity below 10  $\Omega$ cm and saturates over 100  $\Omega$ cm which implies that a high resistivity substrate is a better choice.

Fig. 6. The calculated values of SRF of the spiral inductor shown in Fig. 3 as functions of the uniform substrate resistivity.

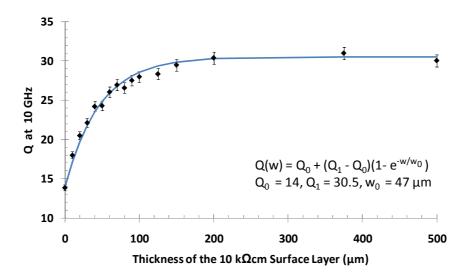

Fig. 7. Calculated Q-factors at 10 GHz for the spiral inductor shown in Fig. 3, but on a bi-layered resistivity (10k/100  $\Omega$ cm) substrate. The Q-factor is plotted as a function of the thickness of the top surface layer while the total substrate thickness is kept fixed at 500  $\mu$ m. The variation in Q has been modelled in the inset.

The important question that arises from the discussion above is that whether a uniformly high resistivity substrate is required to obtain the beneficial improvements in terms of  $Q_{max}$ ,  $f_{max}$  and SRF. A previous work<sup>10</sup> suggested that the field penetrations into the substrates of microstrip lines and coplanar waveguides were different for different substrate resistivities leading to reduced losses for high resistivity substrates. Our simulation results for Q calculated at 10 GHz presented in Fig. 7 for a bilayered resistivity substrate of a total thickness of 500  $\mu$ m clarify the situation for spiral inductors. In these calculations the resistivities of the top layer and the bulk silicon are 10 kΩcm and 100 Ωcm, respectively, and the thickness of the top layer is increased from 0 (entire substrate is 100 Ωcm) to 500  $\mu$ m (entire substrate is 10 kΩcm). It is found that the value of Q starts to saturate to a value of about 30 for a surface layer thickness over 100  $\mu$ m. The trend is modelled with an exponential function, and the characteristic surface layer thickness is found to be 47  $\mu$ m, which appears to be the depth to which the fields penetrate inside the substrate.

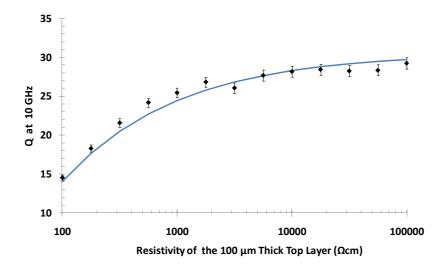

Fig. 8. Calculated Q-factors at 10 GHz for the spiral inductor shown in Fig. 3, but on a bi-layered resistivity substrate. The Q-factor is plotted as a function of the resistivity of the top surface layer (100  $\mu$ m thick) while the bulk of the substrate (400  $\mu$ m thick) is kept fixed at 100  $\Omega$ cm.

In order to optimise the resistivity of the top layer, we calculated the Q-factor at 10 GHz of the spiral inductor as a function of the resistivity of the top layer keeping its thickness fixed at 100  $\mu$ m, and the resistivity of the bulk of the silicon substrate fixed at 100  $\Omega$ cm. The results are presented in Fig. 8. It is found that the Q-factor improves with increase in the resistivity of the top layer monotonically, and nearly saturates for a value of 10 k $\Omega$ cm. This suggests that the bi-layered resistivity silicon substrate improves the performance of spiral inductors optimally, and it is not required to go for uniformly high resistivity substrates.

## Conclusions

We have grown high resistivity Cz-Si substrates of resistivities > 10 k $\Omega$ cm at room temperatures starting from low resistivity (~ 50  $\Omega$ cm) n-type material by implanting gold, which compensates the shallow background carriers in the material by deep level compensation. The technique produces a bi-layered resistivity material with very high resistivity layers near the surfaces and a relatively low resistivity bulk region. We experimentally observed reduced microwave attenuation in the material. Full 3-D electromagnetic simulations of spiral inductors placed on the bi-layered resistivity silicon using the HFSS package show improved values of the Q-factor comparable to values obtained for cases where the entire substrate is uniformly very high resistive. It is found that a surface layer of thickness > about 50  $\mu$ m having a resistivity of more than 10 k $\Omega$ cm is adequate to reap the benefit.

#### Acknowledgement

The authors acknowledge financial support from EPSRC, UK through grants EP/F033311/1 and EP/F035721/1.

## References

- 1. W. Heinrich, J. Gerdes, F. J. Schmuckle, C. Rheinfelder and K. Strohm, IEEE Transactions on Microwave Theory and Techniques 46 (5), 709-712 (1998).

- 2. M. Bulsara, Solid State Technology 51 (3), 42-47, 61 (2008).

- 3. D. M. Jordan, R. H. Haslam, K. Mallik, R. J. Falster and P. R. Wilshaw, Journal of The Electrochemical Society 157 (5), H540-H545 (2010).

- 4. K. Mallik, R. J. Falster and P. R. Wilshaw, Semiconductor Science and Technology 18 (6), 517-524 (2003).

- 5. C. P. Yue and S. S. Wong, IEEE J Solid-State Circuits 33 (5), 743-752 (1998).

- 6. J. Chen and J. J. Liou, Journal of Semiconductor Technology and Science 4 (3), 149-167 (2004).

- 7. S. S. Mohan, M. d. M. Hershenson, S. P. Boyd and T. H. Lee, IEEE J Solid-State Circuits 34 (10), 1419-1424 (1999).

- 8. J. N. Burghartz and B. Rejaei, IEEE Transactions on Electron Devices 50 (3), 718-729 (2003).

- 9. S. J. Pan, L. W. Li and W. Y. Yin, Progress in Electromagnetics Research 45, 123-151 (2004).

- 10. D. Lederer and J. P. Raskin, Solid-State Electronics 47 (11), 1927-1936 (2003).